Torsteuerung

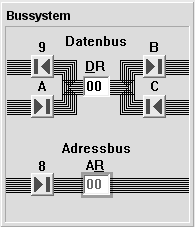

Torsteuerung in MIKROSIM

An Stellen, an denen der Informationsfluss kontrolliert werden muss (vgl. Bild), benötigt man eine Steuerung, mit denen man Daten auf einen „Bus“, eine Leitung, an den mehrere Schaltungen angeschlossen sind, legen kann.

Im Grunde ist solch ein „Bus“ nichts weiter als eine Serie von parallelen Datenleitungen, über die verschiedene Funktionseinheiten („Geräte“) des Computers miteinander kommunizieren. Je mehr Leitungen dazu parallel geschaltet werden, umso mehr Bits können gleichzeitig über diesen Bus übertragen werden. Der klassische ISA-Bus der ersten IBM-PC-Generation (XT) hatte eine Breite von 62 Leitungen, von denen 8 für Daten, 20 für Adressen und die restlichen für Steuerleitungen und Stromversorgung genutzt wurden. Wenn wir uns auf die für den Nutzdaten-Transport reservierten 8 Leitungen beschränken, handelt es sich also um einen „8-Bit-Bus“. Natürlich wurde die Busbreite dann immer weiter vergrößert: auf den 8 Bit breiten „XT-Bus“ folgte der 16 Bit breite „AT-Bus“, welcher wiederum vom 32-Bit breiten „EISA-Bus“ verdrängt wurde, der dann wiederum dem zwar auch nur 32 Bit breiten, dafür aber viel schnelleren „PCI-Bus“ weichen musste usw.

Die verschiedenen Geräte des Computers greifen nun lesend und/oder schreibend auf die einzelnen Busleitungen zu. Betrachten wir exemplarisch nur eine dieser Busleitungen, und stellen wir uns vor, dass zwei Geräte an sie angeschlossen seien. Wenn die beiden Geräte nur Daten vom Bus lesen wollen, dann können sie das ohne Probleme beide gleichzeitig tun: die Busleitung kann an (fast) beliebig viele Lese-Eingänge der Geräte angeschlossen werden!

Problematisch wird es, wenn Geräte Daten auf den Bus schreiben wollen: dann muss nämlich sicher gestellt werden, dass zu jeder Zeit nur (höchstens) ein Gerät schreibend auf den Bus zugreift. Einige der Steuerleitungen der oben beschriebenen historischen Bus-Systeme dienten genau diesem Zweck.

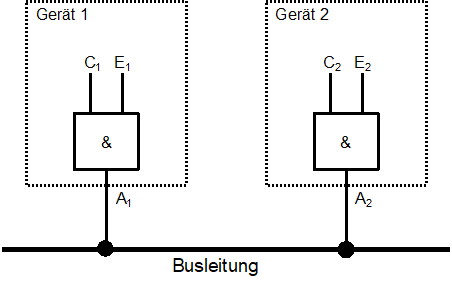

Aber das Problem ist noch ein wenig heimtückischer: Um überhaupt irgendwann auf eine Bus-Leitung schreiben zu können, muss ein Gerät einen Ausgang mit dieser Leitung verbinden. Stellen wir uns für einen Augenblick vor, wir würden das ganz vorsichtig über die eingangs besprochene Tor-Steuerung machen. Dann könnte die Situation etwa so aussehen:

Bus-System mit Torsteuerung - naive Version

Im ersten Gerät liege also das Signal E1 an, das am Ausgang A1 erscheint, wenn das erste Gerät das Schreibrecht hat und C1 = 1 gesetzt ist; im zweiten Gerät liege E2 an, das am Ausgang A2 erscheint, wenn das zweite Gerät das Schreibrecht hat und C2 = 1 gesetzt ist. Solange aber C1 = C2 = 0 ist und kein Gerät schreiben will, ist auch A1 = A2 = 0, und die Welt ist in Ordnung.

Wenn nun das erste Gerät das Schreibrecht anfordert und erhält, dann setzt es C1 = 1, womit dann A1 = E1 auf die Busleitung geschrieben wird. Aber halt! Die Busleitung ist ja ebenfalls noch mit dem Ausgang A2 des Gerätes 2 verbunden, und dort ist ständig A2 = 0! Wenn das erste Gerät die erste 1 auf die Busleitung schreiben will, gibt es eine Katastrophe, weil die Busleitung von zwei Ausgängen mit widersprüchlichen Signalen gefüttert wird: es wird A1 = 1 (Potenzial 5V) und gleichzeitig A2 = 0 (Potenzial 0V) gefordert. Das führt zu einem Kurzschluss!

Dies zeigt, dass wir für einen auf den Bus schreibenden Ausgang mehr Aufwand treiben müssen als eine simple Tor-Steuerung einzusetzen. Die Ausgänge A1 und A2 können nicht einfach normale Ausgänge logischer Gatter sein, welche im deaktivierten Zustand auf einem bestimmten festen Potenzial liegen. Sie müssen stattdessen im inaktiven Zustand erlauben, dass die angeschlossene Busleitung sowohl eine 0 als auch eine 1 transportieren kann. Das ist etwa so, wie wenn A von der Busleitung getrennt wäre. Eine physische Trennung (etwa durch einen mechanischen Schalter oder ein Relais) würde aber den schnellen Zugriff auf den Bus erschweren und verbietet sich damit.

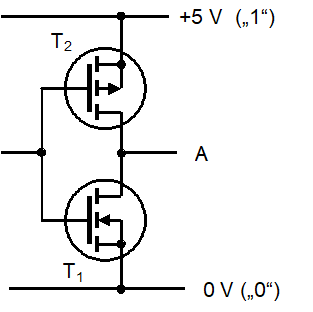

Glücklicherweise bietet die CMOS-Technologie eine elegante Lösung für dieses Problem. Schauen wir uns dazu nochmals einen typischen Gatterausgang in CMOS-Technologie an:

NOT-Schaltung in CMOS-Technologie

Wenn A = 1 ist, dann ist der Drain-Source-Widerstand des unteren Transistors sehr groß, während der des oberen Transistors sehr klein ist. Wenn A = 0 ist, ist es umgekehrt. Der Ausgang ist also stets niederohmig entweder mit der 5-Volt-Leitung oder der 0-Volt-Leitung verbunden, und genau das ist das Übel: im deaktivierten Zustand sollten besser beide Transistoren hochohmig sein – dann könnte das Potenzial der Busleitung einen beliebigen Wert annehmen, obwohl diese noch physisch mit dem (deaktivierten) Ausgang A verbunden ist! Dies ist die gute Idee, die das Problem lösen wird. Wir können dazu aber natürlich nicht mehr beide Transistoren mit demselben Gate-Signal anzusteuern, sondern müssen für jeden Transistor ein eigenes Steuersignal bereitstellen. Das folgende Bild zeigt eine mögliche Schaltung, die das gewünschte leistet:

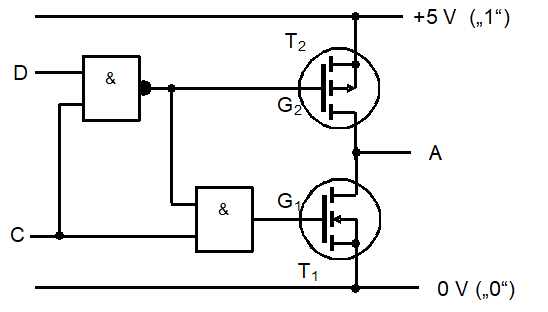

Tri-State-Buffer für Torsteuerung

Am Eingang D liegt das Bit an, das am Ausgang A auf den Bus geschrieben werden soll. Der Eingang C entscheidet, ob die Ausgangsstufe aktiv ist oder nicht: für C = 0 werden beide Ausgangstransistoren in einen hochohmigen Zustand geschaltet und der Ausgang damit deaktiviert, für C = 1 wird er aktiviert und es ist dann A = D. Eine solche Schaltung nennt man ein „Tri-State-Buffer“. Die folgende Wahrheitswert-Tabelle hilft beim Überprüfen der Funktion dieser Schaltung:

| D | C | G2 | G1 | A |

|---|---|---|---|---|

| 0 | 0 | 1 (s) | 0 (s) | Hi-Z |

| 1 | 0 | 1 (s) | 0 (s) | Hi-Z |

| 0 | 1 | 1 (s) | 1 (l) | 0 |

| 1 | 1 | 0 (l) | 0 (s) | 1 |

In der letzten Spalte bezeichnet „Hi-Z“ denjenigen Zustand des Ausgangs A, in dem die beiden Ausgangstransistoren hochohmig sind. Es ist dies der „dritte Zustand“ (neben „0“ und „1“), auf den der Name dieser Schaltung hinweist. Er muss immer dann angenommen werden, wenn das Gerät keinen Schreibzugriff auf die Busleitung hat: wenn beide Ausgangstransistoren hochohmig sind, kann von außen ein beliebiges Potenzial angelegt werden, ohne dass durch die Transistoren rückwärts ein Strom fließt.

Hintergrundinformationen: Herunterladen [odt][4 MB]

Weiter zu Speicherung von Bits